关键词 |

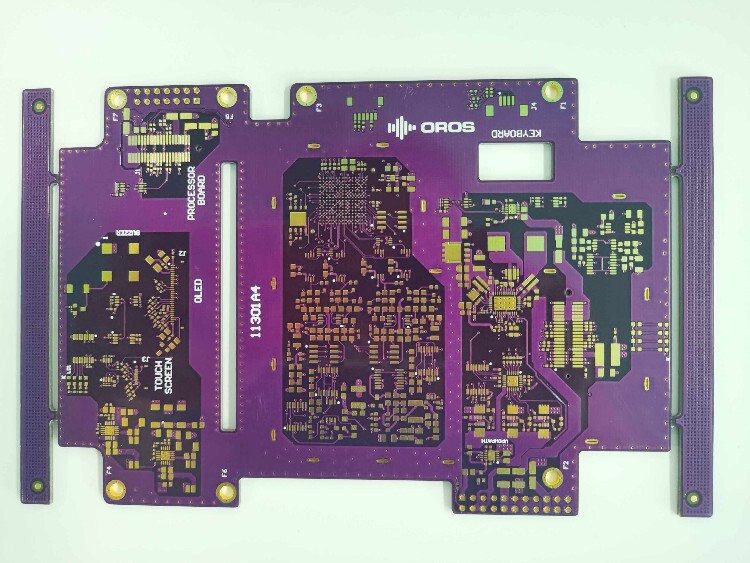

PCB二十层板工厂,4OZ厚铜板PCB厂家,拓展坞PCB厂家,TG260 PCB线路板工厂 |

面向地区 |

阻燃特性 |

VO板 |

|

绝缘层厚度 |

常规板 |

层数 |

多面 |

基材 |

铜 |

绝缘材料 |

有机树脂 |

绝缘树脂 |

环氧树脂(EP) |

软硬结合板的优缺点:

软硬结合板,就是柔性线路板与硬性线路板,经过压合等工序,按相关工艺要求组合在一起,形成的具有FPC特性与PCB特性的线路板。

因为软硬结合板是FPC与PCB的组合,软硬结合板的生产应同时具备FPC生产设备与PCB生产设备。

,由电子工程师根据需求画出软性结合板的线路与外形,然后,下发到可以生产软硬结合板的工厂,经过CAM工程师对相关文件进行处理、规划,然后安排FPC产线生产所需FPC、PCB产线生产PCB,这两款软板与硬板出来后,按照电子工程师的规划要求,将FPC与PCB经过压合机无缝压合,再经过一系列细节环节,终就制成了软硬结合板。

很重要的一个环节,应为软硬结合板难度大,细节问题多,在出货之前,一般都要进行全检,因其价值比较高,以免让供需双方造成相关利益损失。

优点:软硬结合板同时具备FPC的特性与PCB的特性,因此,它可以用于一些有特殊要求的产品之中,既有一定的挠性区域,也有一定的刚性区域,对节省产品内部空间,减少成品体积,提高产品性能有很大的帮助。

缺点:软硬结合板生产工序繁多,生产难度大,良品率较低,所投物料、人力较多,因此,其价格比较贵,生产周期比较长。

高速PCB设计指南之三

第三篇 高速PCB设计

(一)、电子系统设计所面临的挑战

随着系统设计复杂性和集成度的大规模提高,电子系统设计师们正在从事100MHZ以上的电路设计,总线的工作频率也已经达到或者超过50MHZ,有的甚至超过100MHZ。目前约50% 的设计的时钟频率超过50MHz,将近20% 的设计主频超过120MHz。

当系统工作在50MHz时,将产生传输线效应和信号的完整性问题;而当系统时钟达到120MHz时,除非使用高速电路设计知识,否则基于传统方法设计的PCB将无法工作。因此,高速电路设计技术已经成为电子系统设计师采取的设计手段。只有通过使用高速电路设计师的设计技术,才能实现设计过程的可控性。

(二)、什么是高速电路

通常认为如果数字逻辑电路的频率达到或者超过45MHZ~50MHZ,而且工作在这个频率之上的电路已经占到了整个电子系统一定的份量(比如说1/3),就称为高速电路。

实际上,信号边沿的谐波频率比信号本身的频率高,是信号快速变化的上升沿与下降沿(或称信号的跳变)引发了信号传输的非预期结果。因此,通常约定如果线传播延时大于1/2数字信号驱动端的上升时间,则认为此类信号是高速信号并产生传输线效应。

信号的传递发生在信号状态改变的瞬间,如上升或下降时间。信号从驱动端到接收端经过一段固定的时间,如果传输时间小于1/2的上升或下降时间,那么来自接收端的反射信号将在信号改变状态之前到达驱动端。反之,反射信号将在信号改变状态之后到达驱动端。如果反射信号很强,叠加的波形就有可能会改变逻辑状态。

(三)、高速信号的确定

上面我们定义了传输线效应发生的前提条件,但是如何得知线延时是否大于1/2驱动端的信号上升时间?一般地,信号上升时间的典型值可通过器件手册给出,而信号的传播时间在PCB设计中由实际布线长度决定。下图为信号上升时间和允许的布线长度(延时)的对应关系。

PCB 板上每单位英寸的延时为 0.167ns.。但是,如果过孔多,器件管脚多,网线上设置的约束多,延时将增大。通常高速逻辑器件的信号上升时间大约为0.2ns。如果板上有GaAs芯片,则大布线长度为7.62mm。

设Tr为信号上升时间, Tpd 为信号线传播延时。如果Tr≥4Tpd,信号落在安全区域。如果2Tpd≥Tr≥4Tpd,信号落在不确定区域。如果Tr≤2Tpd,信号落在问题区域。对于落在不确定区域及问题区域的信号,应该使用高速布线方法。

(四)、什么是传输线

PCB板上的走线可等效为下图所示的串联和并联的电容、电阻和电感结构。串联电阻的典型值0.25-0.55 ohms/foot,因为绝缘层的缘故,并联电阻阻值通常很高。将寄生电阻、电容和电感加到实际的PCB连线中之后,连线上的终阻抗称为特征阻抗Zo。线径越宽,距电源/地越近,或隔离层的介电常数越高,特征阻抗就越小。如果传输线和接收端的阻抗不匹配,那么输出的电流信号和信号终的稳定状态将不同,这就引起信号在接收端产生反射,这个反射信号将传回信号发射端并再次反射回来。随着能量的减弱反射信号的幅度将减小,直到信号的电压和电流达到稳定。这种效应被称为振荡,信号的振荡在信号的上升沿和下降沿经常可以看到。

(五)、传输线效应

基于上述定义的传输线模型,归纳起来,传输线会对整个电路设计带来以下效应。

· 反射信号Reflected signals

· 延时和时序错误Delay & Timing errors

· 多次跨越逻辑电平门限错误False Switching

· 过冲与下冲Overshoot/Undershoot

· 串扰Induced Noise (or crosstalk)

· 电磁辐射EMI radiation

5.1 反射信号

如果一根走线没有被正确终结(终端匹配),那么来自于驱动端的信号脉冲在接收端被反射,从而引发不预期效应,使信号轮廓失真。当失真变形非常显著时可导致多种错误,引起设计失败。同时,失真变形的信号对噪声的敏感性增加了,也会引起设计失败。如果上述情况没有被足够考虑,EMI将显著增加,这就不单单影响自身设计结果,还会造成整个系统的失败。

反射信号产生的主要原因:过长的走线;未被匹配终结的传输线,过量电容或电感以及阻抗失配。

5.2 延时和时序错误

信号延时和时序错误表现为:信号在逻辑电平的高与低门限之间变化时保持一段时间信号不跳变。过多的信号延时可能导致时序错误和器件功能的混乱。

通常在有多个接收端时会出现问题。电路设计师确定坏情况下的时间延时以确保设计的正确性。信号延时产生的原因:驱动过载,走线过长。

5.3 多次跨越逻辑电平门限错误

信号在跳变的过程中可能多次跨越逻辑电平门限从而导致这一类型的错误。多次跨越逻辑电平门限错误是信号振荡的一种特殊的形式,即信号的振荡发生在逻辑电平门限附近,多次跨越逻辑电平门限会导致逻辑功能紊乱。反射信号产生的原因:过长的走线,未被终结的传输线,过量电容或电感以及阻抗失配。

5.4 过冲与下冲

过冲与下冲来源于走线过长或者信号变化太快两方面的原因。虽然大多数元件接收端有输入保护二极管保护,但有时这些过冲电平会远远超过元件电源电压范围,损坏元器件。

5.5 串扰

串扰表现为在一根信号线上有信号通过时,在PCB板上与之相邻的信号线上就会感应出相关的信号,我们称之为串扰。

信号线距离地线越近,线间距越大,产生的串扰信号越小。异步信号和时钟信号更容易产生串扰。因此解串扰的方法是移开发生串扰的信号或屏蔽被严重干扰的信号。

5.6 电磁辐射

EMI(Electro-Magnetic Interference)即电磁干扰,产生的问题包含过量的电磁辐射及对电磁辐射的敏感性两方面。EMI表现为当数字系统加电运行时,会对周围环境辐射电磁波,从而干扰周围环境中电子设备的正常工作。它产生的主要原因是电路工作频率太高以及布局布线不合理。目前已有进行 EMI仿真的软件工具,但EMI仿真器都很昂贵,仿真参数和边界条件设置又很困难,这将直接影响仿真结果的准确性和实用性。通常的做法是将控制EMI的各项设计规则应用在设计的每一环节,实现在设计各环节上的规则驱动和控制。

(六)、避免传输线效应的方法

针对上述传输线问题所引入的影响,我们从以下几方面谈谈控制这些影响的方法。

6.1 严格控制关键网线的走线长度

如果设计中有高速跳变的边沿,就考虑到在PCB板上存在传输线效应的问题。现在普遍使用的很高时钟频率的快速集成电路芯片更是存在这样的问题。解决这个问题有一些基本原则:如果采用CMOS或TTL电路进行设计,工作频率小于10MHz,布线长度应不大于7英寸。工作频率在50MHz布线长度应不大于1.5英寸。如果工作频率达到或超过75MHz布线长度应在1英寸。对于GaAs芯片大的布线长度应为0.3英寸。如果超过这个标准,就存在传输线的问题。

6.2 合理规划走线的拓扑结构

解决传输线效应的另一个方法是选择正确的布线路径和终端拓扑结构。走线的拓扑结构是指一根网线的布线顺序及布线结构。当使用高速逻辑器件时,除非走线分支长度保持很短,否则边沿快速变化的信号将被信号主干走线上的分支走线所扭曲。通常情形下,PCB走线采用两种基本拓扑结构,即菊花链(Daisy Chain)布线和星形(Star)分布。

对于菊花链布线,布线从驱动端开始,依次到达各接收端。如果使用串联电阻来改变信号特性,串联电阻的位置应该紧靠驱动端。在控制走线的高次谐波干扰方面,菊花链走线效果好。但这种走线方式布通率低,不容易布通。实际设计中,我们是使菊花链布线中分支长度尽可能短,安全的长度值应该是:Stub Delay <= Trt *0.1.

例如,高速TTL电路中的分支端长度应小于1.5英寸。这种拓扑结构占用的布线空间较小并可用单一电阻匹配终结。但是这种走线结构使得在不同的信号接收端信号的接收是不同步的。

星形拓扑结构可以有效的避免时钟信号的不同步问题,但在密度很高的PCB板上手工完成布线十分困难。采用自动布线器是完成星型布线的好的方法。每条分支上都需要终端电阻。终端电阻的阻值应和连线的特征阻抗相匹配。这可通过手工计算,也可通过CAD工具计算出特征阻抗值和终端匹配电阻值。

在上面的两个例子中使用了简单的终端电阻,实际中可选择使用更复杂的匹配终端。种选择是RC匹配终端。RC匹配终端可以减少功率消耗,但只能使用于信号工作比较稳定的情况。这种方式适合于对时钟线信号进行匹配处理。其缺点是RC匹配终端中的电容可能影响信号的形状和传播速度。

串联电阻匹配终端不会产生额外的功率消耗,但会减慢信号的传输。这种方式用于时间延迟影响不大的总线驱动电路。 串联电阻匹配终端的优势还在于可以减少板上器件的使用数量和连线密度。

后一种方式为分离匹配终端,这种方式匹配元件需要放置在接收端附近。其优点是不会拉低信号,并且可以很好的避免噪声。典型的用于TTL输入信号(ACT,HCT, FAST)。

此外,对于终端匹配电阻的封装型式和安装型式也考虑。通常SMD表面贴装电阻比通孔元件具有较低的电感,所以SMD封装元件成为。如果选择普通直插电阻也有两种安装方式可选:垂直方式和水平方式。

垂直安装方式中电阻的一条安装管脚很短,可以减少电阻和电路板间的热阻,使电阻的热量更加容易散发到空气中。但较长的垂直安装会增加电阻的电感。水平安装方式因安装较低有更低的电感。但过热的电阻会出现漂移,在坏的情况下电阻成为开路,造成PCB走线终结匹配失效,成为潜在的失败因素。

6.3 抑止电磁干扰的方法

很好地解决信号完整性问题将改善PCB板的电磁兼容性(EMC)。其中非常重要的是PCB板有很好的接地。对复杂的设计采用一个信号层配一个地线层是十分有效的方法。此外,使电路板的外层信号的密度小也是减少电磁辐射的好方法,这种方法可采用"表面积层"技术"Build-up"设计制做PCB来实现。表面积层通过在普通工艺 PCB 上增加薄绝缘层和用于贯穿这些层的微孔的组合来实现,电阻和电容可埋在表层下,单位面积上的走线密度会增加近一倍,因而可降低 PCB的体积。PCB面积的缩小对走线的拓扑结构有的影响,这意味着缩小的电流回路,缩小的分支走线长度,而电磁辐射近似正比于电流回路的面积;同时小体积特征意味着高密度引脚封装器件可以被使用,这又使得连线长度下降,从而电流回路减小,提高电磁兼容特性。

6.4 其它可采用技术

为减小集成电路芯片电源上的电压瞬时过冲,应该为集成电路芯片添加去耦电容。这可以有效去除电源上的毛刺的影响并减少在印制板上的电源环路的辐射。

当去耦电容直接连接在集成电路的电源管腿上而不是连接在电源层上时,其平滑毛刺的效果好。这就是为什么有一些器件插座上带有去耦电容,而有的器件要求去耦电容距器件的距离要足够的小。

任何高速和高功耗的器件应尽量放置在一起以减少电源电压瞬时过冲。

如果没有电源层,那么长的电源连线会在信号和回路间形成环路,成为辐射源和易感应电路。

走线构成一个不穿过同一网线或其它走线的环路的情况称为开环。如果环路穿过同一网线其它走线则构成闭环。两种情况都会形成天线效应(线天线和环形天线)。天线对外产生EMI辐射,同时自身也是敏感电路。闭环是一个考虑的问题,因为它产生的辐射与闭环面积近似成正比。

结束语

高速电路设计是一个非常复杂的设计过程。本文所阐述的方法就是针对解决这些高速电路设计问题的。此外,在进行高速电路设计时有多个因素需要加以考虑,这些因素有时互相对立。如高速器件布局时位置靠近,虽可以减少延时,但可能产生串扰和显著的热效应。因此在设计中,需权衡各因素,做出全面的折衷考虑;既满足设计要求,又降低设计复杂度。高速PCB设计手段的采用构成了设计过程的可控性,只有可控的,才是可靠的,也才能是成功的!

高精密度(HDI板)电路板的耐热性介绍

HDI板的耐热性能是HDI可靠性能中重要的一个项目,HDI板的板厚变得越来越薄,对其耐热性能的要求也越来越高。无铅化进程的推进,也提高了HDI板耐热性能的要求,而且由于HDI板在层结构等方面不同于普通多层通孔PCB板,因此HDI板的耐热性能与普通多层通孔PCB板相比有所不同,一阶HDI板典型结构。HDI板的耐热性能缺陷主要是爆板和分层。到目前为止,根据多种材料以及多款HDI板的耐热性能测试的经验,发现HDI板发生爆板机率大的区域是密集埋孔的上方以及大铜面的下方区域。

耐热性是指PCB抵抗在焊接过程中产生的热机械应力的能力, PCB在耐热性能测试中发生分层的机制一般包括以下几种:

1) 测试样品内部不同材料在温度变化时,膨胀和收缩性能不同而在样品内部产生内部热机械应力,从而导致裂缝和分层的产生。

2) 测试样品内部的微小缺陷(包括空洞,微裂纹等),是热机械应力集中所在,起到应力的放大器的作用。在样品内部应力的作用下,更加容易导致裂缝或分层的产生。

3) 测试样品中挥发性物质(包括有机挥发成分和水),在高温和剧烈温度变化时,急剧膨胀产生的内部蒸汽压力,当膨胀的蒸汽压力到达测试样品内部的微小缺陷(包括空洞,微裂纹等)时,微小缺陷对应的放大器作用就会导致分层。

HDI板容易在密集埋孔的上方发生分层,这是由于HDI板在埋孔分布区域特殊的结构所导致的。有无埋孔区域的应力分析如下表1。无埋孔区域(结构1)在耐热性能测试受热膨胀时,在同一平面上各个位置的Z方向的膨胀量都是均匀的,因此不会存在由于结构的差异造成的应力集中区域。当区域中设计有埋孔且埋孔钻在基材面上(结构2)时,在埋孔与埋孔之间的A-A截面上,由于基材没有收到埋孔在Z方向的约束,因而膨胀量较大,而在埋孔和焊盘所在的B-B截面上,由于基材受到埋孔在Z方向的约束,因而膨胀量较小,这三处膨胀量的差异,在埋孔焊盘与HDI介质和塞孔树脂交界处和附近区域造成应力集中,从而比较容易形成裂缝和分层。

HDI板容易在外层大铜面的下方发生分层,这是由于在贴装和焊接时,PCB受热,挥发性物质(包括有机挥发成分和水)急剧膨胀,外层大铜面阻挡了挥发性物质(包括有机挥发成分和水)的及时逸出,因此产生的内部蒸汽压力,当膨胀的蒸汽压力到达测试样品内部的微小缺陷(包括空洞,微裂纹等)时,微小缺陷对应的放大器作用就会导致分层。

| 主营行业:PCB电路板 |

| 公司主营:pcb电路板,pcb多层板,hdi线路板,pcb快板 |

| 采购产品:电路板 |

| 主营地区:深圳 |

| 企业类型:私营有限责任公司 |

| 注册资金:人民币1000万 |

| 公司成立时间:2011-07-26 |

| 员工人数:301 - 500 人 |

| 研发部门人数:11 - 50 人 |

| 经营模式:生产型 |

| 经营期限:2011-01-01 至 2052-01-01 |

| 最近年检时间:2022年 |

| 登记机关:深圳市市场监督管理局 |

| 经营范围:电子元器件,电子产品及PCB电路板的销售;国内贸易、货物及技术进出口。(法律、行政法规、国务院决定规定在登记前须经批准的项目除外;涉及行政许可的,须取得行政许可文件后方可经营)^电子产品及电路板的研发,电路板的生产。 |

| 厂房面积:12000平方米 |

| 月产量:20000平方米 |

| 是否提供OEM:是 |

| 质量控制:内部 |

| 公司邮编:518000 |

| 公司电话:0755-27055569 |